# A Microelectronics Curriculum Designed with Industry Input and Project-Based Laboratories

## Jennifer T. Ross Electrical and Computer Engineering Department University of the Pacific

## 1. Introduction

With the changes in the ABET 2000 criteria, universities have considerably more freedom in defining "sufficient" coverage in their curricula. With this freedom comes uncertainty in finding the right mix between depth and breadth for the fast paced microelectronics field. Another issue in preparing students for this field is not only the course content but the work environment they will encounter which involves team projects, technical reporting, problem solving, and massive information processing skills. This paper summarizes two NSF projects geared at these problems. First, a summary from industry partners defining sufficient breadth and depth for undergraduates in the area of microelectronics. Second the development of a new microelectronics laboratory conducted in a "simulated corporate environment", which is designed to prepare students for the environment they will encounter in the workplace in addition to teaching the course material. The new microelectronics laboratory involves the integration of software, measurement tools, and project-based learning. "Project-chips" were developed which reinforce course material, while maintaining the illusion of company products. Students work with the theory, simulation and actual measurements for all major concepts. This paper reports on the industrial panel's input, the course format, the integration of software and measurement tools, the "Project-chips", and how the facade of corporate life is emulated in the classroom. This project was made possible through funding from a Hewlett Packard Education Grant and two NSF grants. An Instrument and Laboratory Improvement (ILI) Grant provided much of the software and equipment for this project, and a Course and Curriculum Development (CCD) grant helped shape the content of the microelectronics curriculum through forming the industrial panel and creating the "Project-chips".

#### 2. Breadth versus Depth

To find the appropriate mix between engineering fundamentals and current technology a panel was formed consisting of engineers from companies related to the integrated circuit industry including: Intel, Advanced Micro Devices, National Semiconductor, Motorola, Hewlett Packard, Digital Equipment Corporation, Silicon Graphics, Altera, Cadence Laboratories, and Mentor Graphics. The panel was designed to incorporate engineers at different stages in their careers and in different areas of the IC industry[1]. The panel was formed as part of a the CCD Grant entitled "Teaching Integrated Circuit Design in a Simulated Corporate Environment". This project included developing material for an undergraduate VLSI design course with a heavy professional component emphasizing team work, communication, presentations, and project based learning [2,3,11].

During the day-long workshop industrial representatives first defined their ideal engineer and then moved on to identify the skills and knowledge base critical to the microelectronics area.

Toward the end of the day, they prioritized these qualities which allowed the author to develop the breadth and depth requirements shown in Table 1.

The interpretation of the data in Table 1 is as follows: 1) Only those skills or experiences specifically requested by the industry representatives (and not academicians) are included, 2) All material in the "Core" section are intended to be taken by every student seeking employment in the microelectronics area; 3) The doted lines in the depth column attempt to separate a digital/analog or process/manufacturing emphasis 4) Students would likely pursue depth in more than one area; 5) Prerequisites to the skills are not specified; 6) No course framework is implied, but could be developed using this list.

By examining Table 1, and in discussions with panel members, there was a real cry for increased breadth! Industry desires students with exposure to a much broader set of skills, which emphasizes the entire product design cycle from concept to manufacturing. (even if it is at a more surface level). For instance, every student should be exposed to system level design, hardware and software integration, and basic architecture, even if their specialization is solid state. And likewise, every student in digital design should understand basic CMOS fabrication process and manufacturing IC's.

The panel deemed that hands on experience with appropriate simulation tools is essential, but students should concentrate on the limitations and abilities of each tool, rather than mechanical use of a system. Particular software packages were discussed, but dedication to one package was discouraged. It was agreed that C++ is the language every student should know today, while Assembly language can be left to electives, or students with a software emphasis.

|                | Breadth (Core)                             | Depth                                                      |

|----------------|--------------------------------------------|------------------------------------------------------------|

| Software       | UNIX operating system, C++ language,       | Algorithms (optimization, AI, list-based interfaces),      |

|                | HDL coding, Layout Tools, Spice            | Programming environments (X, Motif, Visual),               |

|                | modeling, Data structures, Project         | Programming tools (shell scripting, sed, awk, m4 perl),    |

|                | experience.                                | Assembly language, Client/Server, Documentation.           |

| Digital/Analog | System level design, basic architecture &  | FPGA/ ASIC tradeoffs, CAD tools (Schematic capture,        |

| Design         | μ-architecture, clocking strategies, state | static & dynamic timing tools, Place & Route, DRC, back    |

| (Hardware)     | machine design, comb. logic, Karnaugh      | annotation), Verification methodology, Designing for test, |

|                | maps, Analog circuit design & analysis     | Simulation environments, Memory design, Project            |

|                | techniques, Clock skew, Product            | experience from start to finish.                           |

|                | development cycle, Logic synthesis tools   | Cross talk, I/O design, Noise, High speed design           |

|                | (Synopsis), Lab and debugging skills,      | techniques, Communication theory, Power management,        |

|                | Project experience.                        | Wireless (RF) and mixed signal issues, Transmission line   |

|                |                                            | theory, Project experience from start to finish.           |

| Process/       | Product design cycle, Device physics,      | Technology tradeoffs, Process modules (diffusion/ implant, |

| Manufacturing  | Transistor operation (beyond a switch),    | dry & wet etching, deposition, lithography), Fluid         |

|                | Fabrication process, CMOS cross            | dynamics, Material science, Fabrication, equipment,        |

|                | sections, Parasitics, Charge sharing, On-  | Contact issues, Exposure to new technologies (SOI, new     |

|                | chip inductance, Design margins, Power     | memory structures, optoelectronic interconnects)           |

|                | dissipation, Project experience.           | Operations management (plant optimization), Yield          |

|                |                                            | improvement methods (wafer level tests, short loop         |

|                |                                            | monitors, statistical process flow), Process evolution     |

|                |                                            | (scaling and modeling issues).                             |

| Professional   | Communications skills, Project             | Legality and intellectual property rights, engineering     |

| Development    | management, Manufacturing engineering,     | economics, time management, cross cultural interaction,    |

|                | Professional integrity.                    | career planning.                                           |

**Table 1.** Concepts and experiences divided into breadth and depth for undergraduate engineers in the field of microelectronics as dictated by industrial panel.

The panel also placed particular importance on the student's professional development in nontechnical areas, which is increasingly important in today's workplace. When defining the "ideal engineer" the panel's comments mimicked engineering education literature [4,5,6] which stresses the need for an engineer who is innovative, a mentor, a team player/leader, a good communicator, and of course technically competent. Further details of this panel's discussion of the general qualities desired in today's engineer is published elsewhere [7]. Overall there was increased emphasis for universities to take a more active role in the "professional development" of the student, as defined in Table 1.

## 3. Implementation

#### **3.1 Curriculum Level Implementation**

Table 1 serves as a starting place or check point for an educational institution's curricular or course review process for the microelectronics branch. To accomplish the increased breadth that is dictated here, many courses once viewed as electives would be required. Since programs are already at the breaking point in terms of units, requiring additional courses in their present form is unrealistic. To implement a curriculum with increased breadth without additional course requirements the following steps are suggested and are currently being taken at the University of the Pacific. 1) A broader definition of the "core" and streamlined curriculum, which would reduce the repetition of material in "depth" courses, and reduced prerequisite sequences for advanced courses. 2) By identifying computer usage in each course, and monitoring design experiences throughout the curriculum, a broader exposure to software languages and tools can be incorporated. 3) Seeking out science and engineering electives that incorporate more of the manufacturing end of the design cycle outside the Electrical Engineering curriculum and working with those departments to incorporate more IC process examples in their courses. 4) Encompass more of the professional component listed in Table 1, through selected general education classes and a more structured capstone design project including manufacturing, legal, and project management issues.

## 3.2 Course Level Implementation

#### **3.2.1 Project Definition**

Of course the heart of the microelectronics curriculum lies the VLSI course sequence. These courses cover the depth required and provide the project experience desired by industry. At a small university, numerous separate courses in fabrication, analog VLSI, digital VLSI, etc. are not possible, therefore optimal utilization of the student's experience is critical. Input from the industrial panel was used to mold the project-based component of course covering both digital and analog concerns. As part of the CCD grant, project material including simulations, physical layout, and fabrication data, were created for use in a first semester undergraduate VLSI design course and is available on the Web.[10] The goal of these materials is to cover the main concepts, stressing physical layout and design choices, along with team work, and communication skills. The text for the course *is Principles of CMOS VLSI Design - A System Perspective*, by Neil Weste and Kamran Eshraghian, but other similar texts would also work well with the laboratory projects. In fact we use some of the project-chips in the pre-requisite electronics courses. It is the hope that these materials will add to other project based materials to better prepare students for today's microelectronics industry [8]. Two in particular are Robert Caverly's Analog VLSI resource kit [9], and Roger Howe's microelectronics chipset.[12].

## 3.2.2 Project Implementation

The course format is somewhat unique. Students participate as employees of a fictitious ASIC design company, and work through the company's training program and with their products. The "products" are actually chips designed by the instructor[10]. The course is divided into three parts. During the first 6 weeks of the course students are in an intensive training session with fairly traditional lectures and homework assignments to learn the very basic concepts and the needed software. Software for the course include Microsim's Pspice 8.0, Tanner Tools Pro, Altera simulation tools, and Microsoft Office.

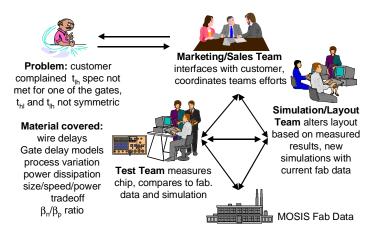

In the second part of the course, students work with the companies products while rotating through one of three teams (Test, Simulation/Layout, Sales/ Marketing). A problem is introduced with one of the company products and the teams decide their own course of action! There are no cookbook labs for this part of the course. For each "product" the teams have the Spice and timing simulations, fabrication data, and physical layout prior to the chip actually being fabricated available off the course web site.[10] Students then measure the actual fabricated chips to discover how physical layout affects performance. Significant course material is introduced through the projects instead of through lectures, and students discover the reasons for differences between predicted and actual performance. Based on their measurements, students decide how to redesign part of the chip to satisfy new project specifications or a change in the fabrication process. Problems are open-ended, so tradeoffs between size, speed and power become apparent. During this session, all teams meet to discuss their status and inter-group communication rules are usually established by the students to help facilitate communication. At the end of each project, each team gives an oral and written report of their work documenting all changes made in layout, simulation, and product documentation. Throughout this part of the course extensive use is made of e-mail and team reports are greatly facilitated by the availability of Microsoft Office on the LAN. At the end of each project, students take a quiz on the subject matter, and individually write evaluations of their team dynamics, their contribution, and the contribution of others. The quiz is used as a portion of their grade, which is independent from the team grade. The team evaluations are used to openly discuss how to improve the team communications, scheduling, and project management issues for the next project. A summary of the three project is listed in Table 2, but change slightly year to year.

Figure 1. Pictorial representation of the project scenario

| Project                                     | Course content covered                                                                   |

|---------------------------------------------|------------------------------------------------------------------------------------------|

| Project 1 - DC MOS operation, Verifying     | Ties physical fabrication quantities (K, V <sub>t</sub> , $\gamma$ , W/L, $\lambda$ ) to |

| fabrication parameters, Noise margins       | MOS inverter properties                                                                  |

| Project 2 - Timing and loading effects      | Examines timing and delay issues, parasitics and loading                                 |

| (examine 4-bit adder, or other basic unit)  | effects, Driving capacitive loads                                                        |

| Project 3 - Speed, Power, and Sizing issues | Tradeoffs between speed and power in moving to smaller                                   |

|                                             | dimensions. Short channel effects                                                        |

Table 2 Brief Summary of "project-chip" concepts

During the final part of the course, students create their own designs ready for submission to the MOSIS fabrication service. They work in teams or alone on a project that they specify, doing layout and simulation. Since the class contains students of both digital and analog emphasis as well as engineering physics students, the final project can be in an area of their interest. With the current funding situation with MOSIS, the course does not rely on fabricating chips through MOSIS only using their fabrication databases, and could continue to operate without fabricating student designs

Several problems arose when implementing the laboratory. Once the previously mentioned software was purchased and installed, it became apparent that students in the Test Team could not take enough measurements in the time frame allowed to meaningfully compare to the Simulation Team results as well as fully characterize the chip's performance. At the time, the lab did not have any automated data acquisition systems. At first the projects were re-examined to reduce the amount of measurements needed, but fortunately a Hewlett Packard Education Grant provided updated millimeters, power supplies, and function generators which can be controlled through GPIB interface. We have since added LabVIEW to the LAN and in addition to automating many of the measurements, are investigating remotely controlled stations through the Internet.

Another problem was refining the project to be completed in the 2 1/2 week time frame, but after three semesters of trial and error an "instructors" guide with hints to keep the students moving was developed including monitoring the flow of e-mail to find bottlenecks quickly. This prodding and spying technique seems to work, allowing the students to finish the project in the specified time frame.

## 3.2.3 Assessment

Assessment techniques to evaluate the effectiveness of the "simulated corporate environment" course format over traditional lecture/laboratory experience included pre and post surveys, student self-assessment, student tracking, and instructor observation. Student's pre and post surveys were designed to measure the student reaction to teamwork, oral presentations, and "level of professionalism". Part of the survey to measure their professional development was designed by Co-PI Gary Martin, Director of Co-op program at University of the Pacific. For this part, students answered essay questions regarding definition to terms like quality, teamwork, etc. The pre and post surveys were compared by outside professionals to see if they could identify which survey was taken before the course versus after the course. The result was documented in a report by Martin, but basically yielded no change in their "level of professionalism". After discussion, it was realized that 90% of the students had already been on one or more cooperative education experiences (a requirement at UOP), so the effect of one 4-unit course would pale in comparison to their co-op experience.

A better indicator of the course effectiveness in preparing students for the field of microelectronics came from the students tracking. Initial student tracking indicates a large jump in students obtaining positions with Intel and Advanced Micro Devices, two companies which we had previously not placed large number of students, yet is physically located relatively close to UOP. The new course stresses how physical layout affect performance but also ties in the big picture of the entire design process from concept to manufacturing. Comparing the three years prior to the course implementation and the three years of graduates going through the course the number of accepted job offers at Intel and AMD rose by 300%. Of those accepting jobs at Intel and AMD, all but two passed through the new course (those two were mechanical engineers). The new course format has been conducted three times over the past 2 1/2 years, and student tracking will be continued. Although the three-fold increase is impressive it should be noted that it is difficult to separate the effect of the course format versus the current industry-hiring trend.

Also through pre and post surveys, students self evaluated their interests, likes, and dislikes regarding team work, oral presentations, using computers, etc. In these surveys, students answered questions on a scale from 1-5 on how strongly they agree or disagree with the statement. On the pretest, 85% of the students strongly agreed (marked 1 or 2) with the statement 'I dislike giving oral presentation", to only 40% strongly agreeing (1 or 2) with the same statement at the end of the course. Students became very proficient in giving talks using Power Point reducing both the preparation time, and logistics of putting together oral and written report with multiple authors. Likewise 80% of the students that had indicated on their pre-test that they "are concerned that your grade relies on the work of others" softened their opinion to a lower "dislike" factor. The projects were designed such that they would require way too much work for one "good" student to complete individually if he/she tried. From written comments they commented that "efficient team work is essential to complete the projects". From comments, it was decided that more effort should go into preparing the students for project management both in developing a reporting scheme, schedule, and communication channels

Student self assessments rank the course as very time consuming, but on the other hand there is definitely a camaraderie which was formed among the teams to "get the job done" which as an instructor is good to see. Hopefully through restructuring of the curriculum some of the material on the course can be moved to pre-requisite courses. A separate paper is being developed addressing assessment issues with project-based work and the role of the team leader, which tries to identify the most effective assessment techniques for this type of teaching.

## **4** Summary

Input from industry is valuable to ensure that a curriculum is developing engineers that have the needed skills and knowledge base to be productive in today's workplace. However, incorporating everything that industrial representatives desire in a graduate is not the way develop a curriculum. Their input must be balanced with the student's overall education. The panel was very in tune with this need and emphasized that the general and professional development component of a student's education, as listed in Table 1, as being critical to their ultimate success and longevity in the microelectronics field.

The VLSI design laboratory is conducted in a "simulated corporate environment" which emphasizes technical communication skills and teamwork. This environment could be adapted to many other laboratory courses, however is especially suited to integrated circuit design since the successful production of any IC chip requires the close working relationship of many corporate divisions on a relatively short time scale.

## **5** Acknowledgments

The author would like to thank each industrial representative for the time and effort dedicated to this project, and the sponsorship of the corporations involved [1]. This project was funded by NSF Course and Curriculum Development Grant # 9555148, and a NSF Instrument and laboratory improvement Grant #9551598. Through a recent Hewlett Packard Education grant the measurement equipment in the microelectronics laboratory was upgraded to permit automated data acquisition.

## References

[1] Compete list of panelist available at: http://www.uop.edu /eng/faculty/ross/nsf/index.html

[2] Jennifer Ross, "A VLSI Design Laboratory Implemented in a Simulated Corporate Environment", ASEE annual conference proceed., Washington, DC June 23, 1996.

[3] Jennifer Ross "Teaching Integrated Circuit Design in a Simulated Corporate Environment" 1996 ASEE/PSW conference proceedings, San Jose CA, April 5, 1996,

[4] "Educating Tomorrow's Engineers", ASEE Prism, p. 10, May/June 1995.

[5] National Society of Professional Engineers, "Report on Surveys of Opinions by Engineering Deans and Employers of Engineering Graduates on the First Professional Degree", no. 3059, pp. 1-15, Nov. 1992.

[6] "Breadth Vs. Depth" ASEE Prism, p. 48, March 1996.

[7] Jennifer Ross, "Industrial Feedback to the Engineering Curriculum", ASEE/PSW conference proceedings, March 14, 1997.

[8] Robert Caverly, Analog VLSI Design Resource Kit, DUE #9215110.

[9] Web index of sample projects for teaching analog and digital VLSI design from universities across the world:

http://www.uop.edu/eng/courses/elec/elec136/projects.html

[10] web page for the course: http://www.uop.edu/eng/courses/elec/elec136/

[11] Jennifer Ross, "Industrial Feedback to the Microelectronics Curriculum", 1997 IEEE Computer Society International Conference on Microelectronics Systems Education (CSICMSE) proceedings, July 21, Arlington, VA 1997.

[12] Roger Howe's project chips affiliated with "Microelectronics and Integrated approach" at:

http://www.prenhall.com/howe/html/labman.html

## **Biography**

Jennifer Ross is the Director of the Engineering Physics program at University of the Pacific and an Assistant Professor in the Electrical and Computer Engineering Department. Jennifer received her Ph.D. and MS in EE from U.C. Berkeley, and her BS in EE from University of Illinois. She teaches in the area of solid state devices, electronic circuits and VLSI design. She has received numerous awards and grants for her innovative teaching in undergraduate education. (http://www.uop.edu/eng/faculty/ross/)