# Linking Simulation Tools to Laboratory Experiments: Teaching Design Verification in Engineering Technology

## Jay R. Porter, James Ochoa, Sanjay Tumati Texas A&M University

#### I. Introduction

The Electronics Engineering Technology (EET) program at Texas A&M University is currently working with industry to incorporate both digital and analog testing techniques into the curriculum. One area that has been identified as important by industry is helping future engineers understand the concept of integrating simulation into the design verification and testing process. This has led to ongoing efforts by the authors to bring simulation into the laboratory in both the analog and digital electronics course sequences.

One approach currently used requires the students to manually use simulation tools while testing their circuits in the laboratory to debug and verify design requirements. A better method, which is currently being developed, is to integrate simulation results directly into the test equipment. This paper will discuss continuing work to integrate simulation into both the digital and the analog laboratory curricula. The authors will discuss new tools that allow direct correlation between simulated and actual circuit responses. These include the integration of Altera's MaxPlus II simulation results for digital systems and Cadence's ORCAD PSpice results for analog systems. It should be noted that while ORCAD could be used for both analog and digital simulations, the authors use MaxPlus II in the digital courses so that simulated circuits can be downloaded to actual devices for testing.

### II. Using Simulation to Verify Design in the Classroom

The typical electronics engineering technology program emphasizes circuit analysis and design in two major areas: analog electronics and digital electronics. In courses emphasizing digital electronics, students are taught analysis and design skills and are asked to apply them to problems from simple combinational logic circuits to more complex problems such as the design of a simple microprocessor. In the analog area, students are taught to work with passive components, semiconductor devices, and more complex analog integrated circuits. They are then asked to use these components to design circuits such as filters, amplifiers, etc... Because of the applied nature of engineering technology, these courses generally have a lab component where concepts taught in the classroom can be reinforced with hands-on experience. Circuits designed on paper are constructed, tested and evaluated.

At a minimum, students verify that the tools and theories they are learning actually work. However, the laboratory setting offers the ability to teach much more. One should be able to expose students to the difference between the ideal and the real world and allow them to try "what-if" scenarios on the bench. More abstract concepts such as signal timing and loading can be explored in digital courses, while the effects of real components with tolerances can be studied on the analog side. Unfortunately, lab time is limited and many of the measurements required to verify analog and digital circuit performance can be very time consuming. This is unfortunate because there is no substitute for experience and students are very limited in how much they can do.

Simulation offers a possible solution to this problem. Today's digital and analog circuit simulators have come a long way. By allowing graphical schematic capture and rapid calculation of circuit responses, students can easily prototype circuits inside and outside of class time. Those students motivated to do so can experiment with different designs and watch the effects of changing components.<sup>1,2</sup> For these reasons, simulation tools have become commonplace in electronics engineering technology. Students are typically required to use them to do homework and prelab write-ups. Unfortunately, these tools are still decoupled from the laboratory. At best, students may be required to plot simulated and measured results together in a lab report; and in most cases, students will only do a visual comparison between simulation and reality.

The authors are currently working on tools to integrate simulation into design verification. Using virtual instrumentation, simulations performed dynamically in the lab are being seamlessly integrated into the measurement process. At the same time, tedious measurements can be automated to reduce debugging time and give the students more time to investigate concepts.

#### III. Implementation

There are a variety of simulators available for teaching analog and digital design. Companies including Cadence and Protel provide analog (and mixed-signal) simulators that allow students to graphically enter schematics and then perform time and frequency domain analyses. On the digital side, simulators are available for testing integrated circuits, programmable logic device (PLD) circuits, and discrete logic circuits. The EET program at Texas A&M focuses on two of these tools. The analog course sequence currently performs simulations with Cadence's ORCAD PSpice while the digital course sequence uses Altera's MaxPlusII PLD software. Fortunately, most simulator tools are comparable in form and function, so it would not be difficult to extend the processes discussed here to other tools.

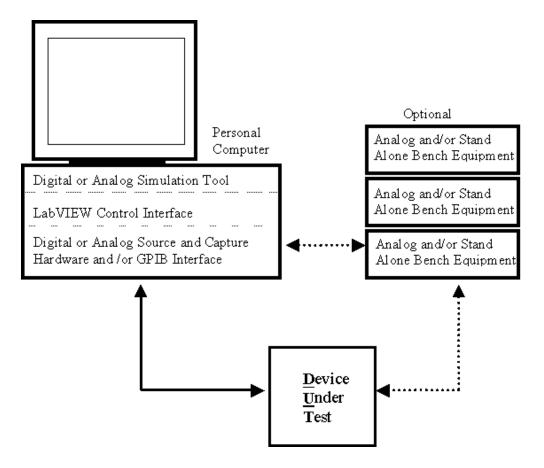

The basic concept is presented in the block diagram in Figure 1. Using a virtual instrumentation tool such as National Instruments' LabVIEW, an integrated measurement and simulation tool can be developed. By using a personal computer at the laboratory bench, students can dynamically model and simulate circuits during lab time. Once the simulation is complete, a virtual instrumentation tool can be

used to access the simulation data. The tool can use this data to determine simulation parameters. These include information such as total simulation time and time step for a transient analysis, frequency range and step size for an AC analysis, functional data for a digital test, and information needed to correlate the data contained in the simulation to actual test points on the circuit. Once the simulation parameters are known, the tool repeats the simulated measurement on the actual circuit using a data acquisition card and/or GPIB controlled instrumentation to automate the procedure. Finally, the simulated and measured data are presented graphically and allow the students to perform real time comparisons.

Figure 1 - Block diagram of the integrated simulation tool.

This system not only helps integrate simulation into the testing and verification of a design, it also allows students to be more efficient by automating and speeding up tedious measurement procedures. For example, verifying the function of a six input digital logic circuit can require sixty-four separate measurements and, at the same time, introduces a significant possibility of error on the part of the student. Through automation, the testing procedure can be done in a matter of seconds. Similarly, a frequency response test that might take the students ten or fifteen minutes can be performed very rapidly

and with more resolution. It should be noted that the authors do not advocate replacing all testing with automated procedures. Having the students manually test a few devices teaches test techniques and debugging skills. However, once the student understands the procedure, rapid automation opens up a whole new area of learning.

Interfacing the virtual instrumentation test tool to the simulator requires a software interface. Fortunately, most simulation tools provide some form of export capability that allows simulation data to be written to an easily understood file format. Cadence PSpice allows data to be exported in an ASCII format file. MaxPlusII supports a similar export capability through a \*.TBL file. In both cases, this is easily accomplished by setting a flag in the simulation tool. An example of this is shown in Figure 2. These files contain information about both the stimulus and the output signals at all relevant points in the circuit. To allow seamless integration of simulation data into virtual instrumentation tools, LabVIEW conversion libraries have been written for these two environments.

| MAX+plus II 7.21 Date: 02/23/99 09:19:38<br>File Generated From: d:\mymaxwork\demoformax\cntdemo.scf                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright (C) 1991-1997 Altera Corporation<br>Any megafunction design,<br>%                                                                                                                                                                                                                                                                                                                                                                       |

| INPUTS UPDOWN SLOAD CNT_EN CLK DATA3 DATA2 DATA1 DATA0;<br>OUTPUTS Q3 Q2 Q1 Q0;<br>UNIT ns;<br>RADIX HEX;<br>PATTERN<br>% U C %<br>% PSN D D D D %<br>% D LT AAAA %<br>% OO_CTTTT %<br>% WAELAAAA QQQQ%<br>% N D N K3210 3210%                                                                                                                                                                                                                    |

| $\begin{array}{c} 0.0 > 0 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 0 \ 0 \\ 10.0 > 0 \ 1 \ 0 \ 1 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 0 \ 0 \\ 11.0 > 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 0 \ 0 \\ 20.0 > 0 \ 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 0 \ 0 \\ 22.5 > 0 \ 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 1 \ 1 \\ 30.0 > 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 1 \ 1 \\ 30.0 > 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ = \ 0 \ 1 \ 1 \\ 45.0 > 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ $ |

Figure 2 – An example of a simulation ouput file. This MaxPlusII \*.TBL file contains simulation data for all inputs and outputs of a circuit. The PSpice simulator exports a similar file.

Using the general implementation scheme discussed in this section, the authors have developed tools for specific analog and digital measurement applications. These tools have been or are being introduced into the classroom. In the following section, two applications currently being implemented are discussed.

### IV. Examples of Integrated Simulation Verification Currently In Use

The Electronics Engineering Technology program at Texas A&M has two major course sequences designed to teach the principles of digital and analog circuit analysis and design. In the digital sequence, students start with a course on the basics of digital design, and then follow it with courses on advanced digital design concepts and microcontroller programming and interfacing concepts. The analog sequence begins with courses on DC and AC circuit analysis and culminates with a course on semiconductor electronics. Both tracks are laboratory intensive, seeking to give students as much hands-on experience as possible. Simulation is routinely used in the laboratory to aid in design verification and debugging. Presented here are two examples of this new thrust to integrate simulation into the test and verification process.

### Digital Design Verification

The digital course sequence currently makes use of an Altera PLD device to implement complex digital circuits designed by the students. A good example of this is in the Advanced Digital Design course where students design and implement a subset of the 6805 microprocessor throughout the course of a semester. The students work in teams to design the different subsystems and then integrate them into a final product at the end of the semester. Because of the complexity of this problem, repeated simulation and testing is critical. To help automate this process, MaxTester was created.<sup>3</sup> MaxTester, developed by an EET undergraduate student, creates an interface between the simulation tools in MaxPlusII and the physical measurement process. First, the student uses MaxPlusII to simulate the circuit to be implemented in the PLD and exports the simulation data in the form of a \*.TBL file. Next, the MaxTester virtual instrument allows the student to import this data through the interface seen in Figure 3.

Once a TBL file is chosen, MaxTester automatically generates test vectors from the simulation data with the correct time scale and makes input/output channel on the digital I/O instrument. A National Instrument's PCI DIO 96 is used as the digital instrument to source test vectors and measure the device under test's output. Finally, MaxTester presents the student with a graphical user interface overlaying the simulated input and output signal with the measured I/O. Figure 4 shows an example of this interface.

The interface also provides cursor and zoom capability so that students can make quantitative measurements. A current drawback of the system is the speed of the PCI DIO 96 card. A new version of MaxTester with updated hardware is planned that will allow students to measure propagation delay and glitches.

| D:\Projects\MaxTester\Max Tester EXE\iosystem.tbl |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| I/O Direction                                     | Channel #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                          |  |  |

| INPUT                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                        |  |  |

| INPUT                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                          |  |  |

| INPUT                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

|                                                   | 000200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |  |  |

|                                                   | and a second sec |                                                                                                                          |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |

| LOOILOI                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                          |  |  |

|                                                   | I/O Direction<br>INPUT<br>INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O Direction Channel #   INPUT 5   INPUT 6   INPUT 7   INPUT 8   INPUT 9   INPUT 10   OUTPUT 17   OUTPUT 19   OUTPUT 20 |  |  |

Figure 3 – MaxTester's simulation interface.

|                                             | R           | AaxTester | IN OUT ALL |

|---------------------------------------------|-------------|-----------|------------|

| 0.00<br>MEMDATO 1<br>MEMDAT1 1<br>MEMDAT2 1 | 1<br>2<br>3 |           |            |

| MEMDAT3 1<br>MEMLD 1<br>CLEAR 1             | 456         |           |            |

| MEMADDRO 1<br>MEMADDR1 1                    | 7           |           |            |

| MEMADDR2 1                                  | 9           |           |            |

| MEMADDR3 1<br>1                             |             |           |            |

| MDOUTO 1                                    | 17          |           |            |

| MDOUT1 1                                    | 18          |           |            |

| MDOUT2 1                                    | 19          |           |            |

| MDOUT3 1                                    | 20          |           |            |

| 1                                           |             |           |            |

Figure 4 – MaxTester's graphical user interface. The red lines indicate simulated signals while black lines indicated measured signals.

### Analog Design Verification

The analog course sequence faces design verification problems similar to those described above. For example, a topic stressed in the AC circuit course and the semiconductor electronics course is that of frequency response, especially in the context of filters. Again, students need to make repeated comparisons between the simulated and measured response of a circuit. For this reason, a new virtual instrumentation tool has been created that allows students to make these comparisons very quickly.

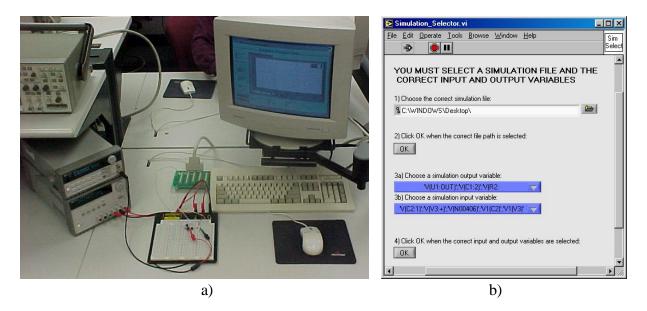

Figure 5a shows the basic test setup. During lab, the students use PSpice to perform a simulation and the data is exported to a ASCII data file. Next, the LabVIEW-based virtual instrument imports this data through the graphical user interface seen in Figure 5b. This interface is flexible in that it allows the user to select any of the voltages or currents in the simulation file to test. Thus, the user can select any two voltages or currents in the circuit to be used as the input and output signals when finding the frequency response.

Figure 5 - a) Hardware setup of the verification tool used for frequency response testing. b) The tool's simulation import interface.

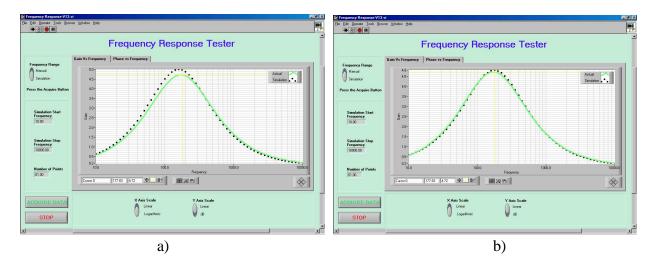

Once the simulation data is imported, the virtual instrument determines the list of test frequencies and begins the measurement. A GPIB controlled Agilent 33120A waveform generator sources the input signal and a National Instruments' 12-bit PCI 6024E digitizes the circuit's input and output. In this manner, performing a frequency response test at sixty separate frequencies takes less than a minute. Once the measurement is complete, the data is processed using Fourier Transform analysis and the amplitude and phase responses of the circuit are calculated. The graphical user interface allows the

student to quantitatively analyze the data. Cursors allow the student to make frequency and voltage measurements. The interface also allows the students to view the output using either linear or logarithmic scales.

Figure 6 shows examples of an active band-pass filter that was tested by the integrated verification tool. In Figure 6a, ideal components were assumed in the simulation. One can see that both the maximum gain and the center frequency are different between the two plots. In Figure 6b, the experiment was run again using actual component values measured on an impedance meter. This time, the tester showed good agreement. An interesting lesson learned here had to do with the capacitors used in the circuit. Because one of them was electrolytic (due to parts availability), good agreement was not reached until both the capacitance and leakage resistance was modeled. This should lead to a good discussion of real components.

Figure 6 - a) The simulated (dashed) and measured (solid) frequency response of an active band-pass filter. The simulation assumed ideal components. b) Same as before but the simulation used actual component values.

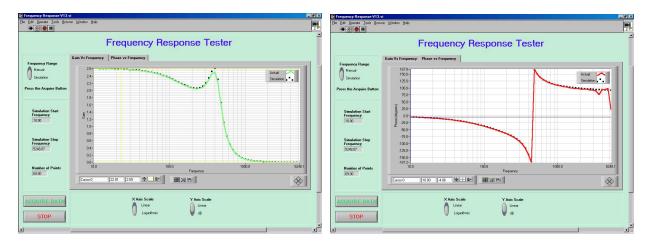

Figure 7 shows a second example of results from the tester. This time, a three pole Chebyshev active filter was implemented and tested. In this case, even reasonable agreement required using actual component values in the simulation. Figure 7 shows the amplitude and phase comparisons produced by the integrated verification tool. One can see very good agreement on both plots; however, the phase plot shows some noise at high frequencies (> 6kHz). This is because the data acquisition card multiplexes between the input and output channels. At high frequencies, the delay between channels becomes noticeable. Certainly one way to fix this problem is to use a data acquisition card that does true simultaneous sampling.

This semester, the integrated verification tool will be introduced into the AC circuit and semiconductor electronics courses. The resultant time savings will be exploited to let the students explore "what-if" senarios in the lab. This will hopefully lead to the students gaining a better understanding of real world circuit design issues.

Figure 7 - Comparison of the amplitude and phase response of a three pole Chebychev active low-pass filter.

### V. Conclusion and Future Work

This paper discusses the development and implementation of measurement tools that can be used to integrate design simulation and verification into a single process. The authors are using the LabVIEW virtual instrumentation programming environment to create measurement tools that seamlessly compare simulation of both analog and digital circuits to measured results. Successful examples have been implemented including a digital stimulus and response tester for PLD circuits and a frequency response tester for analog devices. Both tools will lead to more efficient use of lab time, allowing students to spend more time investigating concepts and less time debugging their measurement system.

Future work includes the development of a "real-time" digital tester that will be able to capture real world phenomena including delay times and glitches. On the analog side, new instrumentation is currently being developed that will allow students to investigate concepts such as analog transients and harmonic distortion. These tools are also being incorporated into ongoing research in mixed-signal and digital test.

Bibliography

- 1. T. Hall, "Using Simulation Software for Electronics Engineering Technology Laboratory Instruction," 2000 American Society of Engineering Education Annual Conference, 3547, St. Louis, MO, June 18-21, 2000.

- 2. S. Pisarski, "Using Simulation Software for Electronics Engineering Technology Laboratory Instruction," *1999 American Society of Engineering Education Annual Conference*, 2548, Charlotte, NC, June 20-23, 1999.

- 3. J. Ochoa, M. Landrum, "An Approach to Advanced Digital Design for Undergraduate Students," ASEE Society of Engineering Education Gulf Southwest Annual Conference, March 7-9, 1999.

#### JAY PORTER

Jay R. Porter joined the Department of Engineering Technology and Industrial Distribution at Texas A&M University in 1998 as an Assistant Professor and currently works in the areas of mixed-signal circuit testing and virtual instrumentation development. He received the BS degree in electrical engineering (1987), the MS degree in physics (1989), and the Ph.D. in electrical engineering (1993) from Texas A&M University.

#### JAMES OCHOA

James Ochoa received a BS degree in electrical engineering at Texas A&M University – Kingsville in 1990 and a Ph.D. in electrical engineering at Texas A&M University in 1999. After completing his Ph.D., he joined the faculty in the Department of Engineering Technology at Texas A&M University. His research activities include digital circuit testing, system-on-a-programmable-chip, and control systems.

#### SANJAY TUMATI

Sanjay Tumati is a student in the Department of Electrical Engineering at Texas A&M and is pursuing his M.S. degree. He is currently teaching analog electronics laboratory classes for the Electronics Engineering Technology Program.